|

| |||

|---|---|---|---|

|

|

||

PROGRAM BLOCK

The module is the basic building block in Verilog which works well for Design. However, for the testbench, a lot of effort is spent getting the environment properly initialized and synchronized, avoiding races between the design and the testbench, automating the generation of input stimuli, and reusing existing models and other infrastructure.

Systemverilog adds a new type of block called program block. It is declared using program and endprogram keywords.

The program block serves these basic purposes:

-> Separates the testbench from the DUT.

-> The program block helps ensure that test bench transitions do not have race conditions with the design

-> It provides an entry point to the execution of testbenches.

-> It creates a scope that encapsulates program-wide data.

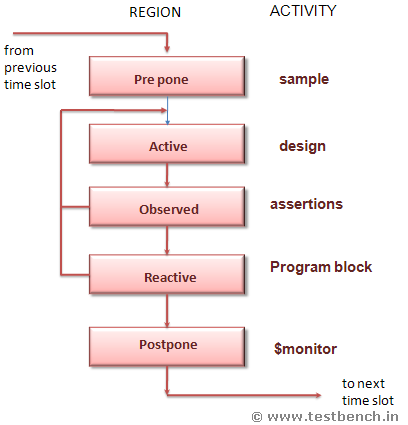

-> It provides a syntactic context that specifies scheduling in the Reactive region which avoids races.

-> It doesnot allow always block. Only initial and methods are allowed, which are more controllable.

-> Each program can be explicitly exited by calling the $exit system task. Unlike $finish, which exits simulation immediately, even if there are pending events.

-> Just like a module, program block has ports. One or more program blocks can be instantiated in a top-level netlist, and connected to the DUT.

The program construct serves as a clear separator between design and testbench, and, more importantly, it specifies specialized execution semantics in the Reactive region for all elements declared within the program. Together with clocking blocks, the program construct provides for race-free interaction between the design and the testbench, and enables cycle and transaction level abstractions.

For example:

program test (input clk, input [16:1] addr, inout [7:0] data);

initial ...

endprogram

program test ( interface device_ifc );

initial ...

endprogram

program schedules events in the Reactive region, the clocking block construct is very useful to automatically sample the steady-state values of previous time steps or clock cycles. Programs that read design values exclusively through clocking blocks with #0 input skews are insensitive to read-write races. It is important to note that simply sampling input signals (or setting non-zero skews on clocking block inputs) does not eliminate the potential for races. Proper input sampling only addresses a single clocking block. With multiple clocks, the arbitrary order in which overlapping or simultaneous clocks are processed is still a potential source for races.

Following example demonstrates the difference between the module based testbench and program based testbenchs.

module DUT();

reg q = 0;

reg clk = 0;

initial

#10 clk = 1;

always @(posedge clk)

q <= 1;

endmodule

module Module_based_TB();

always @ (posedge DUT.clk) $display("Module_based_TB : q = %b\n", DUT.q);

endmodule

program Program_based_TB();

initial

forever @(posedge DUT.clk) $display("Program_based_TB : q = %b\n", DUT.q);

endprogram

RESULT:

Module_based_TB : q = 0

program_based_TB : q = 1

The module is the basic building block in Verilog which works well for Design. However, for the testbench, a lot of effort is spent getting the environment properly initialized and synchronized, avoiding races between the design and the testbench, automating the generation of input stimuli, and reusing existing models and other infrastructure.

Systemverilog adds a new type of block called program block. It is declared using program and endprogram keywords.

The program block serves these basic purposes:

-> Separates the testbench from the DUT.

-> The program block helps ensure that test bench transitions do not have race conditions with the design

-> It provides an entry point to the execution of testbenches.

-> It creates a scope that encapsulates program-wide data.

-> It provides a syntactic context that specifies scheduling in the Reactive region which avoids races.

-> It doesnot allow always block. Only initial and methods are allowed, which are more controllable.

-> Each program can be explicitly exited by calling the $exit system task. Unlike $finish, which exits simulation immediately, even if there are pending events.

-> Just like a module, program block has ports. One or more program blocks can be instantiated in a top-level netlist, and connected to the DUT.

The program construct serves as a clear separator between design and testbench, and, more importantly, it specifies specialized execution semantics in the Reactive region for all elements declared within the program. Together with clocking blocks, the program construct provides for race-free interaction between the design and the testbench, and enables cycle and transaction level abstractions.

For example:

program test (input clk, input [16:1] addr, inout [7:0] data);

initial ...

endprogram

program test ( interface device_ifc );

initial ...

endprogram

program schedules events in the Reactive region, the clocking block construct is very useful to automatically sample the steady-state values of previous time steps or clock cycles. Programs that read design values exclusively through clocking blocks with #0 input skews are insensitive to read-write races. It is important to note that simply sampling input signals (or setting non-zero skews on clocking block inputs) does not eliminate the potential for races. Proper input sampling only addresses a single clocking block. With multiple clocks, the arbitrary order in which overlapping or simultaneous clocks are processed is still a potential source for races.

Following example demonstrates the difference between the module based testbench and program based testbenchs.

module DUT();

reg q = 0;

reg clk = 0;

initial

#10 clk = 1;

always @(posedge clk)

q <= 1;

endmodule

module Module_based_TB();

always @ (posedge DUT.clk) $display("Module_based_TB : q = %b\n", DUT.q);

endmodule

program Program_based_TB();

initial

forever @(posedge DUT.clk) $display("Program_based_TB : q = %b\n", DUT.q);

endprogram

RESULT:

Module_based_TB : q = 0

program_based_TB : q = 1

Index

Introduction

Data Types

Literals

Strings

Userdefined Datatypes

Enumarations

Structures And Uniouns

Typedef

Arrays

Array Methods

Dynamic Arrays

Associative Arrays

Queues

Comparison Of Arrays

Linked List

Casting

Data Declaration

Reg And Logic

Operators 1

Operators 2

Operator Precedency

Events

Control Statements

Program Block

Procedural Blocks

Fork Join

Fork Control

Subroutines

Semaphore

Mailbox

Fine Grain Process Control

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!

Introduction

Data Types

Literals

Strings

Userdefined Datatypes

Enumarations

Structures And Uniouns

Typedef

Arrays

Array Methods

Dynamic Arrays

Associative Arrays

Queues

Comparison Of Arrays

Linked List

Casting

Data Declaration

Reg And Logic

Operators 1

Operators 2

Operator Precedency

Events

Control Statements

Program Block

Procedural Blocks

Fork Join

Fork Control

Subroutines

Semaphore

Mailbox

Fine Grain Process Control

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!