|

| |||

|---|---|---|---|

|

|

||

OPERATORS 1

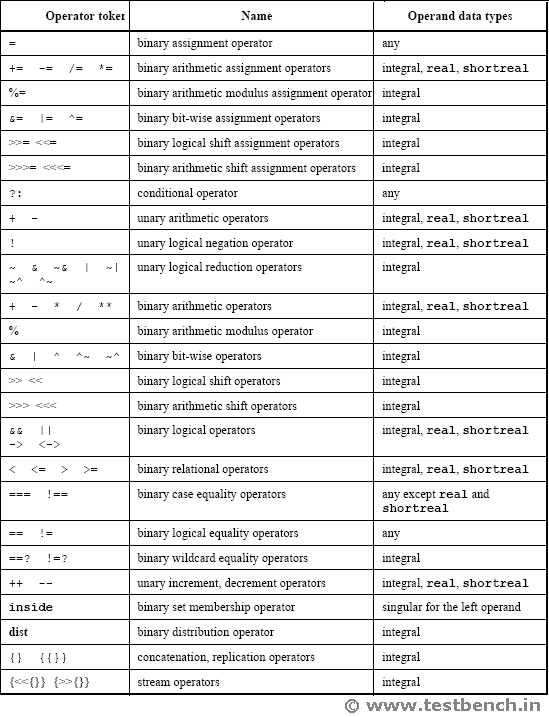

The SystemVerilog operators are a combination of Verilog and C operators. In both languages, the type and size of the operands is fixed, and hence the operator is of a fixed type and size. The fixed type and size of operators is preserved in SystemVerilog. This allows efficient code generation.

Verilog does not have assignment operators or increment and decrement operators. SystemVerilog includes the C assignment operators, such as +=, and the C increment and decrement operators, ++ and --.

Verilog-2001 added signed nets and reg variables, and signed based literals. There is a difference in the rules for combining signed and unsigned integers between Verilog and C. SystemVerilog uses the Verilog rules.

Operators In Systemverilog

Following are the operators in systemverilog

Assignment Operators

In addition to the simple assignment operator, =, SystemVerilog includes the C assignment operators and special bitwise assignment operators:

+=, -=, *=, /=, %=, &=, |=, ^=, <<=, >>=, <<<=,>>>=.

An assignment operator is semantically equivalent to a blocking assignment, with the exception that any left-hand side index expression is only evaluated once.

For example:

a[i]+=2; // same as a[i] = a[i] +2;

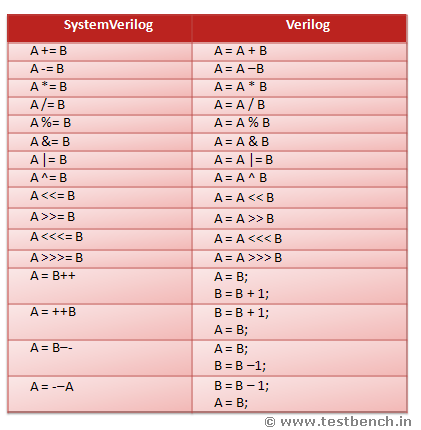

Following are the new SystemVerilog assignment operators and its equivalent in verilog

Assignments In Expression

In SystemVerilog, an expression can include a blocking assignment. such an assignment must be enclosed in parentheses to avoid common mistakes such as using a=b for a==b, or a|=b for a!=b.

if ((a=b)) b = (a+=1); // assign b to a

a = (b = (c = 5));// assign 5 to c

if(a=b) // error in systemverilog

(a=b) statement assigns b value to a and then returns a value.

if((a=b)) is equivalent to

a=b;

if(a)

EXAMPLE

module assignment();

int a,b,c;

initial begin

a = 1; b =2;c =3;

if((a=b))

$display(" a value is %d ",a);

a = (b = (c = 5));

$display(" a is %d b is %d c is %d ",a,b,c);

end

endmodule

RESULT

a value is 2

a is 5 b is 5 c is 5

Concatenation :

{} concatenation right of assignment.

´{} concatenation left of assignment.

EXAMPLE :Concatenation

program main ;

bit [4:0] a;

reg b,c,d;

initial begin

b = 0;

c = 1;

d = 1;

a = {b,c,0,0,d};

{b,c,d} = 3'b111;

$display(" a %b b %b c %b d %b ",a,b,c,d);

end

endprogram

RESULTS

a 00001 b 1 c 1 d 1

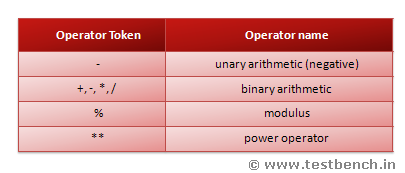

Arithmetic :

EXAMPLE :Arithmetic

program main;

integer a,b;

initial

begin

b = 10;

a = 22;

$display(" -(nagetion) is %0d ",-(a) );

$display(" a + b is %0d ",a+b);

$display(" a - b is %0d ",a-b);

$display(" a * b is %0d ",a*b);

$display(" a / b is %0d ",a/b);

$display(" a modulus b is %0d ",a%b);

end

endprogram

RESULTS

-(nagetion) is -22

a + b is 32

a - b is 12

a * b is 220

a / b is 2

a modules b is 2

Following tabel shows the opwer operator rules for calculating the result.

program main;

integer op1_neg,op1_n1,op1_0,op1_p1,op1_pos;

integer op2_pos_odd,op2_pos_even,op2_zero,op2_neg_odd,op2_neg_even;

initial

begin

op1_neg = -10;op1_n1 = -1;op1_0 = 0;op1_p1 = 1;op1_pos = 10;

op2_pos_odd = 9;op2_pos_even =10;op2_zero=0;op2_neg_odd =-9;op2_neg_even=-10;

$display(" | -10 -1 0 1 10");

$display("---|--------------------------------------------------------");

$display(" 9| %d %d %d %d %d",op1_neg**op2_pos_odd,op1_n1**op2_pos_odd,op1_0**op2_pos_odd,op1_p1**op2_pos_odd,op1_pos**op2_pos_odd);

$display(" 10| %d %d %d %d %d",op1_neg**op2_pos_even,op1_n1**op2_pos_even,op1_0**op2_pos_even,op1_p1**op2_pos_even,op1_pos**op2_pos_even);

$display(" 0| %d %d %d %d %d",op1_neg**op2_zero,op1_n1**op2_zero,op1_0**op2_zero,op1_p1**op2_zero,op1_pos**op2_zero);

$display(" -9| %d %d %d %d %d",op1_neg**op2_neg_odd,op1_n1**op2_neg_odd,op1_0**op2_neg_odd,op1_p1**op2_neg_odd,op1_pos**op2_neg_odd);

$display("-10| %d %d %d %d %d",op1_neg**op2_neg_even,op1_n1**op2_neg_even,op1_0**op2_neg_even,op1_p1**op2_neg_even,op1_pos**op2_neg_even);

end

endprogram

RESULT

| -10 -1 0 1 10

---|--------------------------------------------------------

9| 3294967296 4294967295 0 1 1000000000

10| 1410065408 1 0 1 1410065408

0| 1 1 1 1 1

-9| 0 4294967295 x 1 0

-10| 0 1 x 1 0

Relational :

# > >= < <= relational

EXAMPLE :Relational

program main ;

integer a,b;

initial

begin

b = 10;

a = 22;

$display(" a < b is %0d \n",a < b);

$display(" a > b is %0d \n",a >b);

$display(" a <= b is %0d \n",a <= b);

$display(" a >= b is %0d \n",a >= b);

end

endprogram

RESULTS

a < b is 0

a > b is 1

a <= b is 0

a >= b is 1

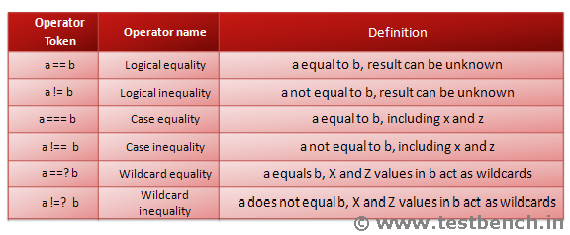

Equality :

The different types of equality (and inequality) operators in SystemVerilog behave differently when their operands contain unknown values (X or Z). The == and != operators may result in X if any of their operands contains an X or Z. The === and !== check the 4-state explicitly, therefore, X and Z values shall either match or mismatch, never resulting in X. The ==? and !=? operators may result in X if the left operand contains an X or Z that is not being compared with a wildcard in the right operand.

EXAMPLE : logical Equality

program main;

reg[3:0] a;

reg[7:0] x, y, z;

initial begin

a = 4'b0101;

x = 8'b1000_0101;

y = 8'b0000_0101;

z = 8'b0xx0_0101;

if (x == a)

$display("x equals a is TRUE.\n");

if (y == a)

$display("y equals a is TRUE.\n");

if (z == a)

$display("z equals a is TRUE.\n");

end

endprogram

RESULTS:

y equals a is TRUE.

EXAMPLE:case equality:

program main ;

reg a_1,a_0,a_x,a_z;

reg b_1,b_0,b_x,b_z;

initial

begin

a_1 = 'b1;a_0 = 'b0;a_x = 'bx;a_z = 'bz;

b_1 = 'b1;b_0 = 'b0;b_x = 'bx;b_z = 'bz;

$display("--------------------------");

$display (" == 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 == b_0,a_0 == b_1,a_0 == b_x,a_0 == b_z);

$display (" 1 %b %b %b %b ",a_1 == b_0,a_1 == b_1,a_1 == b_x,a_1 == b_z);

$display (" x %b %b %b %b ",a_x == b_0,a_x == b_1,a_x == b_x,a_x == b_z);

$display (" z %b %b %b %b ",a_z == b_0,a_z == b_1,a_z == b_x,a_z == b_z);

$display("--------------------------");

$display("--------------------------");

$display (" === 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 === b_0,a_0 === b_1,a_0 === b_x,a_0 === b_z);

$display (" 1 %b %b %b %b ",a_1 === b_0,a_1 === b_1,a_1 === b_x,a_1 === b_z);

$display (" x %b %b %b %b ",a_x === b_0,a_x === b_1,a_x === b_x,a_x === b_z);

$display (" z %b %b %b %b ",a_z === b_0,a_z === b_1,a_z === b_x,a_z === b_z);

$display("--------------------------");

$display("--------------------------");

$display (" =?= 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 =?= b_0,a_0 =?= b_1,a_0 =?= b_x,a_0 =?= b_z);

$display (" 1 %b %b %b %b ",a_1 =?= b_0,a_1 =?= b_1,a_1 =?= b_x,a_1 =?= b_z);

$display (" x %b %b %b %b ",a_x =?= b_0,a_x =?= b_1,a_x =?= b_x,a_x =?= b_z);

$display (" z %b %b %b %b ",a_z =?= b_0,a_z =?= b_1,a_z =?= b_x,a_z =?= b_z);

$display("--------------------------");

$display("--------------------------");

$display (" != 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 != b_0,a_0 != b_1,a_0 != b_x,a_0 != b_z);

$display (" 1 %b %b %b %b ",a_1 != b_0,a_1 != b_1,a_1 != b_x,a_1 != b_z);

$display (" x %b %b %b %b ",a_x != b_0,a_x != b_1,a_x != b_x,a_x != b_z);

$display (" z %b %b %b %b ",a_z != b_0,a_z != b_1,a_z != b_x,a_z != b_z);

$display("--------------------------");

$display("--------------------------");

$display (" !== 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 !== b_0,a_0 !== b_1,a_0 !== b_x,a_0 !== b_z);

$display (" 1 %b %b %b %b ",a_1 !== b_0,a_1 !== b_1,a_1 !== b_x,a_1 !== b_z);

$display (" x %b %b %b %b ",a_x !== b_0,a_x !== b_1,a_x !== b_x,a_x !== b_z);

$display (" z %b %b %b %b ",a_z !== b_0,a_z !== b_1,a_z !== b_x,a_z !== b_z);

$display("--------------------------");

$display("--------------------------");

$display (" !?= 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 !?= b_0,a_0 !?= b_1,a_0 !?= b_x,a_0 !?= b_z);

$display (" 1 %b %b %b %b ",a_1 !?= b_0,a_1 !?= b_1,a_1 !?= b_x,a_1 !?= b_z);

$display (" x %b %b %b %b ",a_x !?= b_0,a_x !?= b_1,a_x !?= b_x,a_x !?= b_z);

$display (" z %b %b %b %b ",a_z !?= b_0,a_z !?= b_1,a_z !?= b_x,a_z !?= b_z);

$display("--------------------------");

end

endprogram

RESULTS

--------------------------

== 0 1 x z

--------------------------

0 1 0 x x

1 0 1 x x

x x x x x

z x x x x

--------------------------

--------------------------

=== 0 1 x z

--------------------------

0 1 0 0 0

1 0 1 0 0

x 0 0 1 0

z 0 0 0 1

--------------------------

--------------------------

=?= 0 1 x z

--------------------------

0 1 0 1 1

1 0 1 1 1

x 1 1 1 1

z 1 1 1 1

--------------------------

--------------------------

!= 0 1 x z

--------------------------

0 0 1 x x

1 1 0 x x

x x x x x

z x x x x

--------------------------

--------------------------

!== 0 1 x z

--------------------------

0 0 1 1 1

1 1 0 1 1

x 1 1 0 1

z 1 1 1 0

--------------------------

--------------------------

!?= 0 1 x z

--------------------------

0 0 1 0 0

1 1 0 0 0

x 0 0 0 0

z 0 0 0 0

--------------------------

The SystemVerilog operators are a combination of Verilog and C operators. In both languages, the type and size of the operands is fixed, and hence the operator is of a fixed type and size. The fixed type and size of operators is preserved in SystemVerilog. This allows efficient code generation.

Verilog does not have assignment operators or increment and decrement operators. SystemVerilog includes the C assignment operators, such as +=, and the C increment and decrement operators, ++ and --.

Verilog-2001 added signed nets and reg variables, and signed based literals. There is a difference in the rules for combining signed and unsigned integers between Verilog and C. SystemVerilog uses the Verilog rules.

Operators In Systemverilog

Following are the operators in systemverilog

Assignment Operators

In addition to the simple assignment operator, =, SystemVerilog includes the C assignment operators and special bitwise assignment operators:

+=, -=, *=, /=, %=, &=, |=, ^=, <<=, >>=, <<<=,>>>=.

An assignment operator is semantically equivalent to a blocking assignment, with the exception that any left-hand side index expression is only evaluated once.

For example:

a[i]+=2; // same as a[i] = a[i] +2;

Following are the new SystemVerilog assignment operators and its equivalent in verilog

Assignments In Expression

In SystemVerilog, an expression can include a blocking assignment. such an assignment must be enclosed in parentheses to avoid common mistakes such as using a=b for a==b, or a|=b for a!=b.

if ((a=b)) b = (a+=1); // assign b to a

a = (b = (c = 5));// assign 5 to c

if(a=b) // error in systemverilog

(a=b) statement assigns b value to a and then returns a value.

if((a=b)) is equivalent to

a=b;

if(a)

EXAMPLE

module assignment();

int a,b,c;

initial begin

a = 1; b =2;c =3;

if((a=b))

$display(" a value is %d ",a);

a = (b = (c = 5));

$display(" a is %d b is %d c is %d ",a,b,c);

end

endmodule

RESULT

a value is 2

a is 5 b is 5 c is 5

Concatenation :

{} concatenation right of assignment.

´{} concatenation left of assignment.

EXAMPLE :Concatenation

program main ;

bit [4:0] a;

reg b,c,d;

initial begin

b = 0;

c = 1;

d = 1;

a = {b,c,0,0,d};

{b,c,d} = 3'b111;

$display(" a %b b %b c %b d %b ",a,b,c,d);

end

endprogram

RESULTS

a 00001 b 1 c 1 d 1

Arithmetic :

EXAMPLE :Arithmetic

program main;

integer a,b;

initial

begin

b = 10;

a = 22;

$display(" -(nagetion) is %0d ",-(a) );

$display(" a + b is %0d ",a+b);

$display(" a - b is %0d ",a-b);

$display(" a * b is %0d ",a*b);

$display(" a / b is %0d ",a/b);

$display(" a modulus b is %0d ",a%b);

end

endprogram

RESULTS

-(nagetion) is -22

a + b is 32

a - b is 12

a * b is 220

a / b is 2

a modules b is 2

Following tabel shows the opwer operator rules for calculating the result.

program main;

integer op1_neg,op1_n1,op1_0,op1_p1,op1_pos;

integer op2_pos_odd,op2_pos_even,op2_zero,op2_neg_odd,op2_neg_even;

initial

begin

op1_neg = -10;op1_n1 = -1;op1_0 = 0;op1_p1 = 1;op1_pos = 10;

op2_pos_odd = 9;op2_pos_even =10;op2_zero=0;op2_neg_odd =-9;op2_neg_even=-10;

$display(" | -10 -1 0 1 10");

$display("---|--------------------------------------------------------");

$display(" 9| %d %d %d %d %d",op1_neg**op2_pos_odd,op1_n1**op2_pos_odd,op1_0**op2_pos_odd,op1_p1**op2_pos_odd,op1_pos**op2_pos_odd);

$display(" 10| %d %d %d %d %d",op1_neg**op2_pos_even,op1_n1**op2_pos_even,op1_0**op2_pos_even,op1_p1**op2_pos_even,op1_pos**op2_pos_even);

$display(" 0| %d %d %d %d %d",op1_neg**op2_zero,op1_n1**op2_zero,op1_0**op2_zero,op1_p1**op2_zero,op1_pos**op2_zero);

$display(" -9| %d %d %d %d %d",op1_neg**op2_neg_odd,op1_n1**op2_neg_odd,op1_0**op2_neg_odd,op1_p1**op2_neg_odd,op1_pos**op2_neg_odd);

$display("-10| %d %d %d %d %d",op1_neg**op2_neg_even,op1_n1**op2_neg_even,op1_0**op2_neg_even,op1_p1**op2_neg_even,op1_pos**op2_neg_even);

end

endprogram

RESULT

| -10 -1 0 1 10

---|--------------------------------------------------------

9| 3294967296 4294967295 0 1 1000000000

10| 1410065408 1 0 1 1410065408

0| 1 1 1 1 1

-9| 0 4294967295 x 1 0

-10| 0 1 x 1 0

Relational :

# > >= < <= relational

EXAMPLE :Relational

program main ;

integer a,b;

initial

begin

b = 10;

a = 22;

$display(" a < b is %0d \n",a < b);

$display(" a > b is %0d \n",a >b);

$display(" a <= b is %0d \n",a <= b);

$display(" a >= b is %0d \n",a >= b);

end

endprogram

RESULTS

a < b is 0

a > b is 1

a <= b is 0

a >= b is 1

Equality :

The different types of equality (and inequality) operators in SystemVerilog behave differently when their operands contain unknown values (X or Z). The == and != operators may result in X if any of their operands contains an X or Z. The === and !== check the 4-state explicitly, therefore, X and Z values shall either match or mismatch, never resulting in X. The ==? and !=? operators may result in X if the left operand contains an X or Z that is not being compared with a wildcard in the right operand.

EXAMPLE : logical Equality

program main;

reg[3:0] a;

reg[7:0] x, y, z;

initial begin

a = 4'b0101;

x = 8'b1000_0101;

y = 8'b0000_0101;

z = 8'b0xx0_0101;

if (x == a)

$display("x equals a is TRUE.\n");

if (y == a)

$display("y equals a is TRUE.\n");

if (z == a)

$display("z equals a is TRUE.\n");

end

endprogram

RESULTS:

y equals a is TRUE.

EXAMPLE:case equality:

program main ;

reg a_1,a_0,a_x,a_z;

reg b_1,b_0,b_x,b_z;

initial

begin

a_1 = 'b1;a_0 = 'b0;a_x = 'bx;a_z = 'bz;

b_1 = 'b1;b_0 = 'b0;b_x = 'bx;b_z = 'bz;

$display("--------------------------");

$display (" == 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 == b_0,a_0 == b_1,a_0 == b_x,a_0 == b_z);

$display (" 1 %b %b %b %b ",a_1 == b_0,a_1 == b_1,a_1 == b_x,a_1 == b_z);

$display (" x %b %b %b %b ",a_x == b_0,a_x == b_1,a_x == b_x,a_x == b_z);

$display (" z %b %b %b %b ",a_z == b_0,a_z == b_1,a_z == b_x,a_z == b_z);

$display("--------------------------");

$display("--------------------------");

$display (" === 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 === b_0,a_0 === b_1,a_0 === b_x,a_0 === b_z);

$display (" 1 %b %b %b %b ",a_1 === b_0,a_1 === b_1,a_1 === b_x,a_1 === b_z);

$display (" x %b %b %b %b ",a_x === b_0,a_x === b_1,a_x === b_x,a_x === b_z);

$display (" z %b %b %b %b ",a_z === b_0,a_z === b_1,a_z === b_x,a_z === b_z);

$display("--------------------------");

$display("--------------------------");

$display (" =?= 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 =?= b_0,a_0 =?= b_1,a_0 =?= b_x,a_0 =?= b_z);

$display (" 1 %b %b %b %b ",a_1 =?= b_0,a_1 =?= b_1,a_1 =?= b_x,a_1 =?= b_z);

$display (" x %b %b %b %b ",a_x =?= b_0,a_x =?= b_1,a_x =?= b_x,a_x =?= b_z);

$display (" z %b %b %b %b ",a_z =?= b_0,a_z =?= b_1,a_z =?= b_x,a_z =?= b_z);

$display("--------------------------");

$display("--------------------------");

$display (" != 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 != b_0,a_0 != b_1,a_0 != b_x,a_0 != b_z);

$display (" 1 %b %b %b %b ",a_1 != b_0,a_1 != b_1,a_1 != b_x,a_1 != b_z);

$display (" x %b %b %b %b ",a_x != b_0,a_x != b_1,a_x != b_x,a_x != b_z);

$display (" z %b %b %b %b ",a_z != b_0,a_z != b_1,a_z != b_x,a_z != b_z);

$display("--------------------------");

$display("--------------------------");

$display (" !== 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 !== b_0,a_0 !== b_1,a_0 !== b_x,a_0 !== b_z);

$display (" 1 %b %b %b %b ",a_1 !== b_0,a_1 !== b_1,a_1 !== b_x,a_1 !== b_z);

$display (" x %b %b %b %b ",a_x !== b_0,a_x !== b_1,a_x !== b_x,a_x !== b_z);

$display (" z %b %b %b %b ",a_z !== b_0,a_z !== b_1,a_z !== b_x,a_z !== b_z);

$display("--------------------------");

$display("--------------------------");

$display (" !?= 0 1 x z ");

$display("--------------------------");

$display (" 0 %b %b %b %b ",a_0 !?= b_0,a_0 !?= b_1,a_0 !?= b_x,a_0 !?= b_z);

$display (" 1 %b %b %b %b ",a_1 !?= b_0,a_1 !?= b_1,a_1 !?= b_x,a_1 !?= b_z);

$display (" x %b %b %b %b ",a_x !?= b_0,a_x !?= b_1,a_x !?= b_x,a_x !?= b_z);

$display (" z %b %b %b %b ",a_z !?= b_0,a_z !?= b_1,a_z !?= b_x,a_z !?= b_z);

$display("--------------------------");

end

endprogram

RESULTS

--------------------------

== 0 1 x z

--------------------------

0 1 0 x x

1 0 1 x x

x x x x x

z x x x x

--------------------------

--------------------------

=== 0 1 x z

--------------------------

0 1 0 0 0

1 0 1 0 0

x 0 0 1 0

z 0 0 0 1

--------------------------

--------------------------

=?= 0 1 x z

--------------------------

0 1 0 1 1

1 0 1 1 1

x 1 1 1 1

z 1 1 1 1

--------------------------

--------------------------

!= 0 1 x z

--------------------------

0 0 1 x x

1 1 0 x x

x x x x x

z x x x x

--------------------------

--------------------------

!== 0 1 x z

--------------------------

0 0 1 1 1

1 1 0 1 1

x 1 1 0 1

z 1 1 1 0

--------------------------

--------------------------

!?= 0 1 x z

--------------------------

0 0 1 0 0

1 1 0 0 0

x 0 0 0 0

z 0 0 0 0

--------------------------

Index

Introduction

Data Types

Literals

Strings

Userdefined Datatypes

Enumarations

Structures And Uniouns

Typedef

Arrays

Array Methods

Dynamic Arrays

Associative Arrays

Queues

Comparison Of Arrays

Linked List

Casting

Data Declaration

Reg And Logic

Operators 1

Operators 2

Operator Precedency

Events

Control Statements

Program Block

Procedural Blocks

Fork Join

Fork Control

Subroutines

Semaphore

Mailbox

Fine Grain Process Control

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!

Introduction

Data Types

Literals

Strings

Userdefined Datatypes

Enumarations

Structures And Uniouns

Typedef

Arrays

Array Methods

Dynamic Arrays

Associative Arrays

Queues

Comparison Of Arrays

Linked List

Casting

Data Declaration

Reg And Logic

Operators 1

Operators 2

Operator Precedency

Events

Control Statements

Program Block

Procedural Blocks

Fork Join

Fork Control

Subroutines

Semaphore

Mailbox

Fine Grain Process Control

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!