|

| |||

|---|---|---|---|

|

|

||

UVM SEQUENCE 2

Pre Defined Sequences:

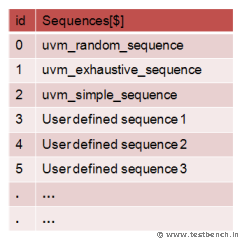

Every sequencer in uvm has 3 pre defined sequences. They are

1)uvm_random_sequence

1)uvm_random_sequence

2)uvm_exhaustive_sequence.

2)uvm_exhaustive_sequence.

3)uvm_simple_sequence

3)uvm_simple_sequence

All the user defined sequences which are registered by user and the above three predefined sequences are stored in sequencer queue.

(S) uvm_random_sequence :

This sequence randomly selects and executes a sequence from the sequencer sequence library, excluding uvm_random_sequence itself, and uvm_exhaustive_sequence. From the above image, from sequence id 2 to till the last sequence, all the sequences are executed randomly. If the "count" variable of the sequencer is set to 0, then non of the sequence is executed. If the "count" variable of the sequencer is set to -1, then some random number of sequences from 0 to "max_random_count" are executed. By default "max_random_count" is set to 10. "Count" and "max_random_count" can be changed using set_config_int().

The sequencer when automatically started executes the sequence which is point by default_sequence. By default default_sequence variable points to uvm_random_sequence.

(S)uvm_exhaustive_sequence:

This sequence randomly selects and executes each sequence from the sequencers sequence library once in a randc style, excluding itself and uvm_random_sequence.

(S)uvm_simple_sequence:

This sequence simply executes a single sequence item.

In the previous example from UVM_SEQUENCE_1 section.

The print() method of the sequencer in that example printed the following

Some observations from the above log:

The count is set to -1. The default sequencer is set to operations_addition. There are 3 predefined sequences and 1 user defined sequence.

Lets look at a example: In the attached example, in file sequence.sv file, there are 4 seuqneces, they are operation_addition, operation_subtraction, operation_multiplication.

In the testcase.sv file, the "default_seuence" is set to "uvm_exhaustive_sequence" using the set_config_string.

set_config_string("sequencer", "default_sequence", "uvm_exhaustive_sequence");

(S)Download the example

uvm_sequence_1.tar

Browse the code in uvm_sequence_1.tar

(S)Command to run the summation

VCS Users : make vcs

Questa Users: make questa

(S)Log File

0: Driving Instruction PUSH_B

10: Driving Instruction PUSH_A

20: Driving Instruction PUSH_B

30: Driving Instruction SUB

40: Driving Instruction POP_C

50: Driving Instruction PUSH_A

60: Driving Instruction PUSH_B

70: Driving Instruction MUL

80: Driving Instruction POP_C

90: Driving Instruction PUSH_A

100: Driving Instruction PUSH_B

110: Driving Instruction ADD

120: Driving Instruction POP_C

From the above log , we can see that all the 3 user defined sequences and predefined uvm_simple_sequence are executed.

Sequence Action Macro:

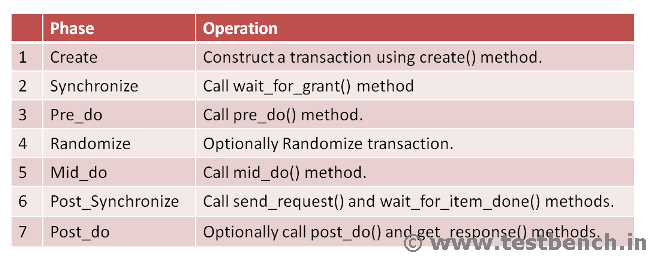

In the previous sections, we have seen the implementation of body() method of sequence. The body() method implementation requires some steps. We have seen these steps as Creation of item, wait for grant, randomize the item, send the item.

All these steps have be automated using "sequence action macros". There are some more additional steps added in these macros. Following are the steps defined with the "sequence action macro".

Pre_do(), mid_do() and post_do() are callback methods which are in uvm sequence. If user is interested , he can use these methods. For example, in mid_do() method, user can print the transaction or the randomized transaction can be fined tuned. These methods should not be clled by user directly.

(S)Syntax:

virtual task pre_do(bit is_item)

virtual function void mid_do(uvm_sequence_item this_item)

virtual function void post_do(uvm_sequence_item this_item)

Pre_do() is a task , if the method consumes simulation cycles, the behavior may be unexpected.

Example Of Pre_do,Mid_do And Post_do

Lets look at a example: We will define a sequence using `uvm_do macro. This macro has all the above defined phases.

1)Define the body method using the `uvm_do() macro. Before and after this macro, just call messages.

virtual task body();

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : Before uvm_do macro ",UVM_LOW);

`uvm_do(req);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : After uvm_do macro ",UVM_LOW);

endtask

2)Define pre_do() method. Lets just print a message from this method.

virtual task pre_do(bit is_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : PRE_DO ",UVM_LOW);

endtask

3)Define mid_do() method. Lets just print a message from this method.

virtual function void mid_do(uvm_sequence_item this_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : MID_DO ",UVM_LOW);

endfunction

4)Define post_do() method. Lets just print a message from this method.

virtual function void post_do(uvm_sequence_item this_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : POST_DO ",UVM_LOW);

endfunction

(S)Complet sequence code:

class demo_uvm_do extends uvm_sequence #(instruction);

instruction req;

function new(string name="demo_uvm_do");

super.new(name);

endfunction

`uvm_sequence_utils(demo_uvm_do, instruction_sequencer)

virtual task pre_do(bit is_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : PRE_DO ",UVM_LOW);

endtask

virtual function void mid_do(uvm_sequence_item this_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : MID_DO ",UVM_LOW);

endfunction

virtual function void post_do(uvm_sequence_item this_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : POST_DO ",UVM_LOW);

endfunction

virtual task body();

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : Before uvm_do macro ",UVM_LOW);

`uvm_do(req);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : After uvm_do macro ",UVM_LOW);

endtask

endclass

(S)Download the example

uvm_sequence_2.tar

Browse the code in uvm_sequence_2.tar

(S)Command to run the simulation

VCS Users : make vcs

Questa Users: make questa

(S)Log file report:

UVM_INFO@0:reporter[sequencer.demo_uvm_do]

Seuqnce Action Macro Phase : Before uvm_do macro

UVM_INFO@0:reporter[sequencer.demo_uvm_do]

Seuqnce Action Macro Phase : PRE_DO

UVM_INFO@0:reporter[sequencer.demo_uvm_do]

Seuqnce Action Macro Phase : MID_DO

0: Driving Instruction MUL

UVM_INFO@10:reporter[sequencer.demo_uvm_do]

Seuqnce Action Macro Phase : POST_DO

UVM_INFO@10:reporter[sequencer.demo_uvm_do]

Seuqnce Action Macro Phase : After uvm_do macro

The above log file shows the messages from pre_do,mid_do and post_do methods.

List Of Sequence Action Macros:

These macros are used to start sequences and sequence items that were either registered with a <`uvm-sequence_utils> macro or whose associated sequencer was already set using the <set_sequencer> method.

(S)`uvm_create(item/sequence)

This action creates the item or sequence using the factory. Only the create phase will be executed.

(S)`uvm_do(item/sequence)

This macro takes as an argument a uvm_sequence_item variable or sequence . All the above defined 7 phases will be executed.

(S)`uvm_do_with(item/sequence, Constraint block)

This is the same as `uvm_do except that the constraint block in the 2nd argument is applied to the item or sequence in a randomize with statement before execution.

(S)`uvm_send(item/sequence)

Create phase and randomize phases are skipped, rest all the phases will be executed. Using `uvm_create, create phase can be executed. Essentially, an `uvm_do without the create or randomization.

(S)`uvm_rand_send(item/sequence)

Only create phase is skipped. rest of all the phases will be executed. User should use `uvm_create to create the sequence or item.

(S)`uvm_rand_send_with(item/sequence , Constraint block)

Only create phase is skipped. rest of all the phases will be executed. User should use `uvm_create to create the sequence or item. Constraint block will be applied which randomization.

(S)`uvm_do_pri(item/sequence, priority )

This is the same as `uvm_do except that the sequence item or sequence is executed with the priority specified in the argument.

(S)`uvm_do_pri_with(item/sequence , constraint block , priority)

This is the same as `uvm_do_pri except that the given constraint block is applied to the item or sequence in a randomize with statement before execution.

(S)`uvm_send_pri(item/sequence,priority)

This is the same as `uvm_send except that the sequence item or sequence is executed with the priority specified in the argument.

(S)`uvm_rand_send_pri(item/sequence,priority)

This is the same as `uvm_rand_send except that the sequence item or sequence is executed with the priority specified in the argument.

(S)`uvm_rand_send_pri_with(item/sequence,priority,constraint block)

This is the same as `uvm_rand_send_pri except that the given constraint block is applied to the item or sequence in a randomize with statement before execution.

Following macros are used on sequence or sequence items on a different sequencer.

(S)`uvm_create_on(item/sequence,sequencer)

This is the same as `uvm_create except that it also sets the parent sequence to the sequence in which the macro is invoked, and it sets the sequencer to the specified sequencer argument.

(S)`uvm_do_on(item/sequence,sequencer)

This is the same as `uvm_do except that it also sets the parent sequence to the sequence in which the macro is invoked, and it sets the sequencer to the specified sequencer argument.

(S)`uvm_do_on_pri(item/sequence,sequencer, priority)

This is the same as `uvm_do_pri except that it also sets the parent sequence to the sequence in which the macro is invoked, and it sets the sequencer to the specified sequencer argument.

(S)`uvm_do_on_with(item/sequence,sequencer, constraint block)

This is the same as `uvm_do_with except that it also sets the parent sequence to the sequence in which the macro is invoked, and it sets the sequencer to the specified sequencer argument. The user must supply brackets around the constraints.

(S)`uvm_do_on_pri_with(item/sequence,sequencer,priority,constraint block)

This is the same as `uvm_do_pri_with except that it also sets the parent sequence to the sequence in which the macro is invoked, and it sets the sequencer to the specified sequencer argument.

Examples With Sequence Action Macros:

virtual task body();

uvm_report_info(get_full_name(),

"Executing Sequence Action Macro uvm_do",UVM_LOW);

`uvm_do(req)

endtask

virtual task body();

uvm_report_info(get_full_name(),

"Executing Sequence Action Macro uvm_do_with ",UVM_LOW);

`uvm_do_with(req,{ inst == ADD; })

endtask

virtual task body();

uvm_report_info(get_full_name(),

"Executing Sequence Action Macro uvm_create and uvm_send",UVM_LOW);

`uvm_create(req)

req.inst = instruction::PUSH_B;

`uvm_send(req)

endtask

virtual task body();

uvm_report_info(get_full_name(),

"Executing Sequence Action Macro uvm_create and uvm_rand_send",UVM_LOW);

`uvm_create(req)

`uvm_rand_send(req)

endtask

(S)Download the example

uvm_sequence_3.tar

Browse the code in uvm_sequence_3.tar

(S)Command to sun the simulation

VCS Users : make vcs

Questa Users: make questa

(S)Log file report

0: Driving Instruction PUSH_B

UVM_INFO@10:reporter[***]Executing Sequence Action Macro uvm_do_with

10: Driving Instruction ADD

UVM_INFO@20:reporter[***]Executing Sequence Action Macro uvm_create and uvm_send

20: Driving Instruction PUSH_B

UVM_INFO@30:reporter[***]Executing Sequence Action Macro uvm_do

30: Driving Instruction DIV

UVM_INFO@40:reporter[***]Executing Sequence Action Macro uvm_create and uvm_rand_send

40: Driving Instruction MUL

Pre Defined Sequences:

Every sequencer in uvm has 3 pre defined sequences. They are

All the user defined sequences which are registered by user and the above three predefined sequences are stored in sequencer queue.

(S) uvm_random_sequence :

This sequence randomly selects and executes a sequence from the sequencer sequence library, excluding uvm_random_sequence itself, and uvm_exhaustive_sequence. From the above image, from sequence id 2 to till the last sequence, all the sequences are executed randomly. If the "count" variable of the sequencer is set to 0, then non of the sequence is executed. If the "count" variable of the sequencer is set to -1, then some random number of sequences from 0 to "max_random_count" are executed. By default "max_random_count" is set to 10. "Count" and "max_random_count" can be changed using set_config_int().

The sequencer when automatically started executes the sequence which is point by default_sequence. By default default_sequence variable points to uvm_random_sequence.

(S)uvm_exhaustive_sequence:

This sequence randomly selects and executes each sequence from the sequencers sequence library once in a randc style, excluding itself and uvm_random_sequence.

(S)uvm_simple_sequence:

This sequence simply executes a single sequence item.

In the previous example from UVM_SEQUENCE_1 section.

The print() method of the sequencer in that example printed the following

----------------------------------------------------------------------

Name Type Size Value

----------------------------------------------------------------------

sequencer instruction_sequen+ - sequencer@2

rsp_export uvm_analysis_export - rsp_export@4

seq_item_export uvm_seq_item_pull_+ - seq_item_export@28

default_sequence string 18 operation_addition

count integral 32 -1

max_random_count integral 32 'd10

sequences array 4 -

[0] string 19 uvm_random_sequence

[1] string 23 uvm_exhaustive_sequ+

[2] string 19 uvm_simple_sequence

[3] string 18 operation_addition

max_random_depth integral 32 'd4

num_last_reqs integral 32 'd1

num_last_rsps integral 32 'd1

----------------------------------------------------------------------

Some observations from the above log:

The count is set to -1. The default sequencer is set to operations_addition. There are 3 predefined sequences and 1 user defined sequence.

Lets look at a example: In the attached example, in file sequence.sv file, there are 4 seuqneces, they are operation_addition, operation_subtraction, operation_multiplication.

In the testcase.sv file, the "default_seuence" is set to "uvm_exhaustive_sequence" using the set_config_string.

set_config_string("sequencer", "default_sequence", "uvm_exhaustive_sequence");

(S)Download the example

uvm_sequence_1.tar

Browse the code in uvm_sequence_1.tar

(S)Command to run the summation

VCS Users : make vcs

Questa Users: make questa

(S)Log File

0: Driving Instruction PUSH_B

10: Driving Instruction PUSH_A

20: Driving Instruction PUSH_B

30: Driving Instruction SUB

40: Driving Instruction POP_C

50: Driving Instruction PUSH_A

60: Driving Instruction PUSH_B

70: Driving Instruction MUL

80: Driving Instruction POP_C

90: Driving Instruction PUSH_A

100: Driving Instruction PUSH_B

110: Driving Instruction ADD

120: Driving Instruction POP_C

From the above log , we can see that all the 3 user defined sequences and predefined uvm_simple_sequence are executed.

Sequence Action Macro:

In the previous sections, we have seen the implementation of body() method of sequence. The body() method implementation requires some steps. We have seen these steps as Creation of item, wait for grant, randomize the item, send the item.

All these steps have be automated using "sequence action macros". There are some more additional steps added in these macros. Following are the steps defined with the "sequence action macro".

Pre_do(), mid_do() and post_do() are callback methods which are in uvm sequence. If user is interested , he can use these methods. For example, in mid_do() method, user can print the transaction or the randomized transaction can be fined tuned. These methods should not be clled by user directly.

(S)Syntax:

virtual task pre_do(bit is_item)

virtual function void mid_do(uvm_sequence_item this_item)

virtual function void post_do(uvm_sequence_item this_item)

Pre_do() is a task , if the method consumes simulation cycles, the behavior may be unexpected.

Example Of Pre_do,Mid_do And Post_do

Lets look at a example: We will define a sequence using `uvm_do macro. This macro has all the above defined phases.

1)Define the body method using the `uvm_do() macro. Before and after this macro, just call messages.

virtual task body();

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : Before uvm_do macro ",UVM_LOW);

`uvm_do(req);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : After uvm_do macro ",UVM_LOW);

endtask

2)Define pre_do() method. Lets just print a message from this method.

virtual task pre_do(bit is_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : PRE_DO ",UVM_LOW);

endtask

3)Define mid_do() method. Lets just print a message from this method.

virtual function void mid_do(uvm_sequence_item this_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : MID_DO ",UVM_LOW);

endfunction

4)Define post_do() method. Lets just print a message from this method.

virtual function void post_do(uvm_sequence_item this_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : POST_DO ",UVM_LOW);

endfunction

(S)Complet sequence code:

class demo_uvm_do extends uvm_sequence #(instruction);

instruction req;

function new(string name="demo_uvm_do");

super.new(name);

endfunction

`uvm_sequence_utils(demo_uvm_do, instruction_sequencer)

virtual task pre_do(bit is_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : PRE_DO ",UVM_LOW);

endtask

virtual function void mid_do(uvm_sequence_item this_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : MID_DO ",UVM_LOW);

endfunction

virtual function void post_do(uvm_sequence_item this_item);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : POST_DO ",UVM_LOW);

endfunction

virtual task body();

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : Before uvm_do macro ",UVM_LOW);

`uvm_do(req);

uvm_report_info(get_full_name(),

"Seuqnce Action Macro Phase : After uvm_do macro ",UVM_LOW);

endtask

endclass

(S)Download the example

uvm_sequence_2.tar

Browse the code in uvm_sequence_2.tar

(S)Command to run the simulation

VCS Users : make vcs

Questa Users: make questa

(S)Log file report:

UVM_INFO@0:reporter[sequencer.demo_uvm_do]

Seuqnce Action Macro Phase : Before uvm_do macro

UVM_INFO@0:reporter[sequencer.demo_uvm_do]

Seuqnce Action Macro Phase : PRE_DO

UVM_INFO@0:reporter[sequencer.demo_uvm_do]

Seuqnce Action Macro Phase : MID_DO

0: Driving Instruction MUL

UVM_INFO@10:reporter[sequencer.demo_uvm_do]

Seuqnce Action Macro Phase : POST_DO

UVM_INFO@10:reporter[sequencer.demo_uvm_do]

Seuqnce Action Macro Phase : After uvm_do macro

The above log file shows the messages from pre_do,mid_do and post_do methods.

List Of Sequence Action Macros:

These macros are used to start sequences and sequence items that were either registered with a <`uvm-sequence_utils> macro or whose associated sequencer was already set using the <set_sequencer> method.

(S)`uvm_create(item/sequence)

This action creates the item or sequence using the factory. Only the create phase will be executed.

(S)`uvm_do(item/sequence)

This macro takes as an argument a uvm_sequence_item variable or sequence . All the above defined 7 phases will be executed.

(S)`uvm_do_with(item/sequence, Constraint block)

This is the same as `uvm_do except that the constraint block in the 2nd argument is applied to the item or sequence in a randomize with statement before execution.

(S)`uvm_send(item/sequence)

Create phase and randomize phases are skipped, rest all the phases will be executed. Using `uvm_create, create phase can be executed. Essentially, an `uvm_do without the create or randomization.

(S)`uvm_rand_send(item/sequence)

Only create phase is skipped. rest of all the phases will be executed. User should use `uvm_create to create the sequence or item.

(S)`uvm_rand_send_with(item/sequence , Constraint block)

Only create phase is skipped. rest of all the phases will be executed. User should use `uvm_create to create the sequence or item. Constraint block will be applied which randomization.

(S)`uvm_do_pri(item/sequence, priority )

This is the same as `uvm_do except that the sequence item or sequence is executed with the priority specified in the argument.

(S)`uvm_do_pri_with(item/sequence , constraint block , priority)

This is the same as `uvm_do_pri except that the given constraint block is applied to the item or sequence in a randomize with statement before execution.

(S)`uvm_send_pri(item/sequence,priority)

This is the same as `uvm_send except that the sequence item or sequence is executed with the priority specified in the argument.

(S)`uvm_rand_send_pri(item/sequence,priority)

This is the same as `uvm_rand_send except that the sequence item or sequence is executed with the priority specified in the argument.

(S)`uvm_rand_send_pri_with(item/sequence,priority,constraint block)

This is the same as `uvm_rand_send_pri except that the given constraint block is applied to the item or sequence in a randomize with statement before execution.

Following macros are used on sequence or sequence items on a different sequencer.

(S)`uvm_create_on(item/sequence,sequencer)

This is the same as `uvm_create except that it also sets the parent sequence to the sequence in which the macro is invoked, and it sets the sequencer to the specified sequencer argument.

(S)`uvm_do_on(item/sequence,sequencer)

This is the same as `uvm_do except that it also sets the parent sequence to the sequence in which the macro is invoked, and it sets the sequencer to the specified sequencer argument.

(S)`uvm_do_on_pri(item/sequence,sequencer, priority)

This is the same as `uvm_do_pri except that it also sets the parent sequence to the sequence in which the macro is invoked, and it sets the sequencer to the specified sequencer argument.

(S)`uvm_do_on_with(item/sequence,sequencer, constraint block)

This is the same as `uvm_do_with except that it also sets the parent sequence to the sequence in which the macro is invoked, and it sets the sequencer to the specified sequencer argument. The user must supply brackets around the constraints.

(S)`uvm_do_on_pri_with(item/sequence,sequencer,priority,constraint block)

This is the same as `uvm_do_pri_with except that it also sets the parent sequence to the sequence in which the macro is invoked, and it sets the sequencer to the specified sequencer argument.

Examples With Sequence Action Macros:

virtual task body();

uvm_report_info(get_full_name(),

"Executing Sequence Action Macro uvm_do",UVM_LOW);

`uvm_do(req)

endtask

virtual task body();

uvm_report_info(get_full_name(),

"Executing Sequence Action Macro uvm_do_with ",UVM_LOW);

`uvm_do_with(req,{ inst == ADD; })

endtask

virtual task body();

uvm_report_info(get_full_name(),

"Executing Sequence Action Macro uvm_create and uvm_send",UVM_LOW);

`uvm_create(req)

req.inst = instruction::PUSH_B;

`uvm_send(req)

endtask

virtual task body();

uvm_report_info(get_full_name(),

"Executing Sequence Action Macro uvm_create and uvm_rand_send",UVM_LOW);

`uvm_create(req)

`uvm_rand_send(req)

endtask

(S)Download the example

uvm_sequence_3.tar

Browse the code in uvm_sequence_3.tar

(S)Command to sun the simulation

VCS Users : make vcs

Questa Users: make questa

(S)Log file report

0: Driving Instruction PUSH_B

UVM_INFO@10:reporter[***]Executing Sequence Action Macro uvm_do_with

10: Driving Instruction ADD

UVM_INFO@20:reporter[***]Executing Sequence Action Macro uvm_create and uvm_send

20: Driving Instruction PUSH_B

UVM_INFO@30:reporter[***]Executing Sequence Action Macro uvm_do

30: Driving Instruction DIV

UVM_INFO@40:reporter[***]Executing Sequence Action Macro uvm_create and uvm_rand_send

40: Driving Instruction MUL

Index

Introduction

Uvm Testbench

Uvm Reporting

Uvm Transaction

Uvm Configuration

Uvm Factory

Uvm Sequence 1

Uvm Sequence 2

Uvm Sequence 3

Uvm Sequence 4

Uvm Sequence 5

Uvm Sequence 6

Uvm Tlm 1

Uvm Tlm 2

Uvm Callback

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!

Introduction

Uvm Testbench

Uvm Reporting

Uvm Transaction

Uvm Configuration

Uvm Factory

Uvm Sequence 1

Uvm Sequence 2

Uvm Sequence 3

Uvm Sequence 4

Uvm Sequence 5

Uvm Sequence 6

Uvm Tlm 1

Uvm Tlm 2

Uvm Callback

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!