|

| |||

|---|---|---|---|

|

|

||

UVM TLM 2

Analysis

The analysis port is used to perform non-blocking broadcasts of transactions. It is by components like monitors/drivers to publish transactions to its subscribers, which are typically scoreboards and response/coverage collectors. For each port, more than one component can be connected. Even if a component is not connected to the port, simulation can continue, unlike put/get ports where simulation is not continued.

The uvm_analysis_port consists of a single function, write(). Subscriber component should provide an implementation of write()method. UVM provides the uvm_subscriber base component to simplify this operation, so a typical analysis component would extend uvm_subscriber and its export is analysis_export.

Lets write a example.

In the example, we will define a monitor component and a subscriber.

(S)Monitor source code:

In monitor, call the function write() pass the transaction.

class monitor extends uvm_monitor;

uvm_analysis_port #(instruction) anls_port;

function new(string name, uvm_component p = null);

super.new(name,p);

anls_port = new("anls_port", this);

endfunction

task run;

instruction inst;

inst = new();

#10ns;

inst.inst = instruction::MUL;

anls_port.write(inst);

#10ns;

inst.inst = instruction::ADD;

anls_port.write(inst);

#10ns;

inst.inst = instruction::SUB;

anls_port.write(inst);

endtask

endclass

(S)Subscriber source code:

In Subscriber, define the write() method.

class subscriber extends uvm_subscriber#(instruction);

function new(string name, uvm_component p = null);

super.new(name,p);

endfunction

function void write(instruction t);

`uvm_info(get_full_name(),

$sformatf("receiving %s",t.inst.name()), UVM_MEDIUM)

endfunction

endclass : subscriber

(S)Env source code:

class env extends uvm_env;

monitor mon;

subscriber sb,cov;

function new(string name = "env");

super.new(name);

mon = new("mon", this);

sb = new("sb", this);

cov = new("cov", this);

endfunction

function void connect();

mon.anls_port.connect(sb.analysis_export);

mon.anls_port.connect(cov.analysis_export);

endfunction

task run();

#1000;

global_stop_request();

endtask

endclass

module test;

env e;

initial begin

e = new();

run_test();

end

endmodule

(S)Download the example

uvm_tlm_3.tar

Browse the code in uvm_tlm_3.tar

(S)Command to sun the simulation

VCS Users : make vcs

Questa Users: make questa

From the below log, you see that transaction is sent to both the components cov and sb.

(S)Log

UVM_INFO subscriber.sv(18) @ 0: env.cov [env.cov] receiving MUL

UVM_INFO subscriber.sv(18) @ 0: env.sb [env.sb] receiving MUL

UVM_INFO subscriber.sv(18) @ 0: env.cov [env.cov] receiving ADD

UVM_INFO subscriber.sv(18) @ 0: env.sb [env.sb] receiving ADD

UVM_INFO subscriber.sv(18) @ 0: env.cov [env.cov] receiving SUB

UVM_INFO subscriber.sv(18) @ 0: env.sb [env.sb] receiving SUB

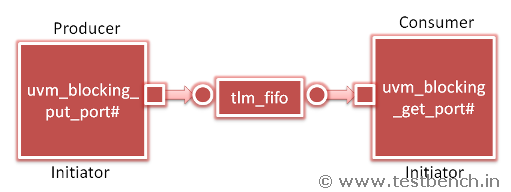

Tlm Fifo

Tlm_fifo provides storage of transactions between two independently running processes just like mailbox. Transactions are put into the FIFO via the put_export and fetched from the get_export.

(S)Methods

Following are the methods defined for tlm fifo.

function new(string name,

uvm_component parent = null,

int size = 1)

The size indicates the maximum size of the FIFO; a value of zero indicates no upper bound.

virtual function int size()

Returns the capacity of the FIFO. 0 indicates the FIFO capacity has no limit.

virtual function int used()

Returns the number of entries put into the FIFO.

virtual function bit is_empty()

Returns 1 when there are no entries in the FIFO, 0 otherwise.

virtual function bit is_full()

Returns 1 when the number of entries in the FIFO is equal to its size, 0 otherwise.

virtual function void flush()

Removes all entries from the FIFO, after which used returns 0 and is_empty returns 1.

Example

Lets implement a example.

In this example, we will use a tlm_fifo to connect producer and consumer.

The producer component generates the transaction and using its put_port pot() method, sends transaction out. The consumer component, to get the transaction from outside, uses get() method of get_port. These two ports are connected to tlm_fifo in the env class. In this example, producer and consumer are initiators as both components are calling the methods.

(S)Producer source code:

class producer extends uvm_component;

uvm_blocking_put_port#(int) put_port;

function new(string name, uvm_component p = null);

super.new(name,p);

put_port = new("put_port", this);

endfunction

task run;

int randval;

for(int i = 0; i < 10; i++)

begin

#10;

randval = $urandom_range(4,10);

`uvm_info("producer",

$sformatf("sending %d",randval), UVM_MEDIUM)

put_port.put(randval);

end

endtask

endclass : producer

(S)Consumer source code:

class consumer extends uvm_component;

uvm_blocking_get_port#(int) get_port;

function new(string name, uvm_component p = null);

super.new(name,p);

get_port = new("get_port", this);

endfunction

task run;

int val;

forever

begin

get_port.get(val);

`uvm_info("consumer",

$sformatf("receiving %d", val), UVM_MEDIUM)

end

endtask

endclass : consumer

(S)Env source code:

class env extends uvm_env;

producer p;

consumer c;

tlm_fifo #(int) f;

function new(string name = "env");

super.new(name);

p = new("producer", this);

c = new("consumer", this);

f = new("fifo", this);

endfunction

function void connect();

p.put_port.connect(f.put_export);

c.get_port.connect(f.get_export);

endfunction

task run();

#1000 global_stop_request();

endtask

endclass

(S)Download the example

uvm_tlm_4.tar

Browse the code in uvm_tlm_4.tar

(S)Command to sun the simulation

VCS Users : make vcs

Questa Users: make questa

(S)Log

UVM_INFO producer.sv(28) @ 10: env.producer [producer] sending 7

UVM_INFO consumer.sv(26) @ 10: env.consumer [consumer] receiving 7

UVM_INFO producer.sv(28) @ 20: env.producer [producer] sending 4

UVM_INFO consumer.sv(26) @ 20: env.consumer [consumer] receiving 4

Analysis

The analysis port is used to perform non-blocking broadcasts of transactions. It is by components like monitors/drivers to publish transactions to its subscribers, which are typically scoreboards and response/coverage collectors. For each port, more than one component can be connected. Even if a component is not connected to the port, simulation can continue, unlike put/get ports where simulation is not continued.

The uvm_analysis_port consists of a single function, write(). Subscriber component should provide an implementation of write()method. UVM provides the uvm_subscriber base component to simplify this operation, so a typical analysis component would extend uvm_subscriber and its export is analysis_export.

Lets write a example.

In the example, we will define a monitor component and a subscriber.

(S)Monitor source code:

In monitor, call the function write() pass the transaction.

class monitor extends uvm_monitor;

uvm_analysis_port #(instruction) anls_port;

function new(string name, uvm_component p = null);

super.new(name,p);

anls_port = new("anls_port", this);

endfunction

task run;

instruction inst;

inst = new();

#10ns;

inst.inst = instruction::MUL;

anls_port.write(inst);

#10ns;

inst.inst = instruction::ADD;

anls_port.write(inst);

#10ns;

inst.inst = instruction::SUB;

anls_port.write(inst);

endtask

endclass

(S)Subscriber source code:

In Subscriber, define the write() method.

class subscriber extends uvm_subscriber#(instruction);

function new(string name, uvm_component p = null);

super.new(name,p);

endfunction

function void write(instruction t);

`uvm_info(get_full_name(),

$sformatf("receiving %s",t.inst.name()), UVM_MEDIUM)

endfunction

endclass : subscriber

(S)Env source code:

class env extends uvm_env;

monitor mon;

subscriber sb,cov;

function new(string name = "env");

super.new(name);

mon = new("mon", this);

sb = new("sb", this);

cov = new("cov", this);

endfunction

function void connect();

mon.anls_port.connect(sb.analysis_export);

mon.anls_port.connect(cov.analysis_export);

endfunction

task run();

#1000;

global_stop_request();

endtask

endclass

module test;

env e;

initial begin

e = new();

run_test();

end

endmodule

(S)Download the example

uvm_tlm_3.tar

Browse the code in uvm_tlm_3.tar

(S)Command to sun the simulation

VCS Users : make vcs

Questa Users: make questa

From the below log, you see that transaction is sent to both the components cov and sb.

(S)Log

UVM_INFO subscriber.sv(18) @ 0: env.cov [env.cov] receiving MUL

UVM_INFO subscriber.sv(18) @ 0: env.sb [env.sb] receiving MUL

UVM_INFO subscriber.sv(18) @ 0: env.cov [env.cov] receiving ADD

UVM_INFO subscriber.sv(18) @ 0: env.sb [env.sb] receiving ADD

UVM_INFO subscriber.sv(18) @ 0: env.cov [env.cov] receiving SUB

UVM_INFO subscriber.sv(18) @ 0: env.sb [env.sb] receiving SUB

Tlm Fifo

Tlm_fifo provides storage of transactions between two independently running processes just like mailbox. Transactions are put into the FIFO via the put_export and fetched from the get_export.

(S)Methods

Following are the methods defined for tlm fifo.

function new(string name,

uvm_component parent = null,

int size = 1)

The size indicates the maximum size of the FIFO; a value of zero indicates no upper bound.

virtual function int size()

Returns the capacity of the FIFO. 0 indicates the FIFO capacity has no limit.

virtual function int used()

Returns the number of entries put into the FIFO.

virtual function bit is_empty()

Returns 1 when there are no entries in the FIFO, 0 otherwise.

virtual function bit is_full()

Returns 1 when the number of entries in the FIFO is equal to its size, 0 otherwise.

virtual function void flush()

Removes all entries from the FIFO, after which used returns 0 and is_empty returns 1.

Example

Lets implement a example.

In this example, we will use a tlm_fifo to connect producer and consumer.

The producer component generates the transaction and using its put_port pot() method, sends transaction out. The consumer component, to get the transaction from outside, uses get() method of get_port. These two ports are connected to tlm_fifo in the env class. In this example, producer and consumer are initiators as both components are calling the methods.

(S)Producer source code:

class producer extends uvm_component;

uvm_blocking_put_port#(int) put_port;

function new(string name, uvm_component p = null);

super.new(name,p);

put_port = new("put_port", this);

endfunction

task run;

int randval;

for(int i = 0; i < 10; i++)

begin

#10;

randval = $urandom_range(4,10);

`uvm_info("producer",

$sformatf("sending %d",randval), UVM_MEDIUM)

put_port.put(randval);

end

endtask

endclass : producer

(S)Consumer source code:

class consumer extends uvm_component;

uvm_blocking_get_port#(int) get_port;

function new(string name, uvm_component p = null);

super.new(name,p);

get_port = new("get_port", this);

endfunction

task run;

int val;

forever

begin

get_port.get(val);

`uvm_info("consumer",

$sformatf("receiving %d", val), UVM_MEDIUM)

end

endtask

endclass : consumer

(S)Env source code:

class env extends uvm_env;

producer p;

consumer c;

tlm_fifo #(int) f;

function new(string name = "env");

super.new(name);

p = new("producer", this);

c = new("consumer", this);

f = new("fifo", this);

endfunction

function void connect();

p.put_port.connect(f.put_export);

c.get_port.connect(f.get_export);

endfunction

task run();

#1000 global_stop_request();

endtask

endclass

(S)Download the example

uvm_tlm_4.tar

Browse the code in uvm_tlm_4.tar

(S)Command to sun the simulation

VCS Users : make vcs

Questa Users: make questa

(S)Log

UVM_INFO producer.sv(28) @ 10: env.producer [producer] sending 7

UVM_INFO consumer.sv(26) @ 10: env.consumer [consumer] receiving 7

UVM_INFO producer.sv(28) @ 20: env.producer [producer] sending 4

UVM_INFO consumer.sv(26) @ 20: env.consumer [consumer] receiving 4

Index

Introduction

Uvm Testbench

Uvm Reporting

Uvm Transaction

Uvm Configuration

Uvm Factory

Uvm Sequence 1

Uvm Sequence 2

Uvm Sequence 3

Uvm Sequence 4

Uvm Sequence 5

Uvm Sequence 6

Uvm Tlm 1

Uvm Tlm 2

Uvm Callback

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!

Introduction

Uvm Testbench

Uvm Reporting

Uvm Transaction

Uvm Configuration

Uvm Factory

Uvm Sequence 1

Uvm Sequence 2

Uvm Sequence 3

Uvm Sequence 4

Uvm Sequence 5

Uvm Sequence 6

Uvm Tlm 1

Uvm Tlm 2

Uvm Callback

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!