|

| |||

|---|---|---|---|

|

|

||

SELF CHECKING TESTBENCHS

A self-checking TestBench checks expected results against actual results obtained from the simulation. Although Self-checking testbenchs require considerably more effort during the initial test bench creation phase, this technique can dramatically Reduce the amount of effort needed to re-check a design after a change has been made to the DUT. Debugging time is significantly shortened by useful error-tracking information that can be built into the TestBench to show where a design fails.

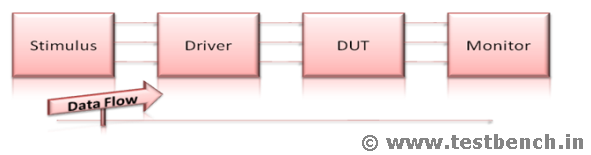

A self-checking TestBench has two major parts, the input blocks and output blocks.

Input block consist of stimulus and driver to drive the stimulus to DUT. The output block consists of monitor to collect the DUT outputs and verify them.

All the above approaches require the test writer to create an explicit test for each feature of the design. Verification approach in which each feature is written in a separate test case file is called directed verification.

EXAMPLE: adder example

module adder(a,b,c); //DUT code start

input [15:0] a,b;

output [16:0] c;

assign c = a + b;

endmodule //DUT code end

module top(); //TestBench code start

reg [15:0] a;

reg [15:0] b;

wire [16:0] c;

adder DUT(a,b,c); //DUT Instantiation

initial

repeat(100) begin

a = $random; //apply random stimulus

b = $random;

#10

$display(" a=%0d,b=%0d,c=%0d",a,b,c);

if( a + b != c) // monitor logic.

$display(" *ERROR* ");

end

endmodule //TestBench code end

A self-checking TestBench checks expected results against actual results obtained from the simulation. Although Self-checking testbenchs require considerably more effort during the initial test bench creation phase, this technique can dramatically Reduce the amount of effort needed to re-check a design after a change has been made to the DUT. Debugging time is significantly shortened by useful error-tracking information that can be built into the TestBench to show where a design fails.

A self-checking TestBench has two major parts, the input blocks and output blocks.

Input block consist of stimulus and driver to drive the stimulus to DUT. The output block consists of monitor to collect the DUT outputs and verify them.

All the above approaches require the test writer to create an explicit test for each feature of the design. Verification approach in which each feature is written in a separate test case file is called directed verification.

EXAMPLE: adder example

module adder(a,b,c); //DUT code start

input [15:0] a,b;

output [16:0] c;

assign c = a + b;

endmodule //DUT code end

module top(); //TestBench code start

reg [15:0] a;

reg [15:0] b;

wire [16:0] c;

adder DUT(a,b,c); //DUT Instantiation

initial

repeat(100) begin

a = $random; //apply random stimulus

b = $random;

#10

$display(" a=%0d,b=%0d,c=%0d",a,b,c);

if( a + b != c) // monitor logic.

$display(" *ERROR* ");

end

endmodule //TestBench code end

Index

Asic Design

Bottle Neck In Asic Flow

Functional Verification Need

Testbench

Linear Testbench

Linear Random Testbench

How To Check The Results

Self Checking Testbenchs

How To Get Scenarios Which We Never Thought

How To Check Whether The Testbench Has Satisfactorily Exercised The Design

Types Of Code Coverage

Statement Coverage

Block Coverage

Conditional Coverage

Branch Coverage

Path Coverage

Toggle Coverage

Fsm Coverage

Make Your Goal 100 Percent Code Coverage Nothing Less

Functional Coverage

Coverage Driven Constraint Random Verification Architecture

Phases Of Verification

Ones Counter Example

Verification Plan

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!

Asic Design

Bottle Neck In Asic Flow

Functional Verification Need

Testbench

Linear Testbench

Linear Random Testbench

How To Check The Results

Self Checking Testbenchs

How To Get Scenarios Which We Never Thought

How To Check Whether The Testbench Has Satisfactorily Exercised The Design

Types Of Code Coverage

Statement Coverage

Block Coverage

Conditional Coverage

Branch Coverage

Path Coverage

Toggle Coverage

Fsm Coverage

Make Your Goal 100 Percent Code Coverage Nothing Less

Functional Coverage

Coverage Driven Constraint Random Verification Architecture

Phases Of Verification

Ones Counter Example

Verification Plan

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!