|

| |||

|---|---|---|---|

|

|

||

PHASE 9 COVERAGE

In this phase we will write the functional coverage for switch protocol. Functional coverage is written in DrvrCovCallback.sv file. After running simulation, you will analyze the coverage results and find out if some test scenarios have not been exercised and write tests to exercise them.

The points which we need to cover are

1) Cover all the port address configurations.

2) Cover all the packet lengths.

3) Cover all correct and incorrect length fields.

4) Cover good and bad FCS.

5) Cover all the above combinations.

We will do the coverage sampling in the driver porst_trans() callback method which we developed in PHASE_6.

1) Define a cover group with following cover points. Define this cover group in a class which extends Driver_callbacks.

class DrvrCovCallback extends Driver_callbacks;

a) All packet lengths:

length : coverpoint pkt.length;

b) All port address:

da : coverpoint pkt.da {

bins p0 = { `P0 };

bins p1 = { `P1 };

bins p2 = { `P2 };

bins p3 = { `P3 }; }

c) Correct and incorrect Length field types:

length_kind : coverpoint pkt.length_kind;

d) Good and Bad FCS:

fcs_kind : coverpoint pkt.fcs_kind;

5) Cross product of all the above cover points:

all_cross: cross length,da,length_kind,fcs_kind;

2) In constructor method, construct the cover group

function new();

switch_coverage = new();

endfunction : new

3) Write task which calls the sample method to cover the points.

task sample(packet pkt);

this.pkt = pkt;

switch_coverage.sample();

endtask:sample

Source Code Of Coverage Class:

`ifndef GUARD_DRVR_CALLBACK_1

`define GUARD_DRVR_CALLBACK_1

class DrvrCovCallback extends Driver_callbacks;

Packet pkt;

covergroup switch_coverage;

length : coverpoint pkt.length;

da : coverpoint pkt.da {

bins p0 = { `P0 };

bins p1 = { `P1 };

bins p2 = { `P2 };

bins p3 = { `P3 }; }

length_kind : coverpoint pkt.length_kind;

fcs_kind : coverpoint pkt.fcs_kind;

all_cross: cross length,da,length_kind,fcs_kind;

endgroup

function new();

switch_coverage = new();

endfunction : new

virtual task post_trans(Packet pkt);

this.pkt = pkt;

switch_coverage.sample();

endtask: post_trans

endclass:DrvrCovCallback

`endif

Now we will connect this callback instance to the Driver.

1) Take the instance of DrvrCovCallback in the Environemtn class.

DrvrCovCallback cov_cb;

2) Construct the cov_cb object in build method.

cov_cb = new();

3) In the Build method, call the append_callback() of the drvr and pass the cov_cb

object.

drvr.append_callback(cov_cb);

(S)Source code of the Environment class:

`ifndef GUARD_ENV

`define GUARD_ENV

class Environment extends vmm_env;

virtual mem_interface.MEM mem_intf ;

virtual input_interface.IP input_intf ;

virtual output_interface.OP output_intf[4] ;

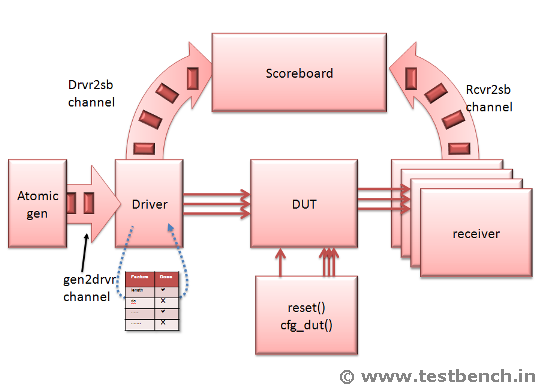

Packet_atomic_gen atomic_gen;

Driver drvr;

Receiver rcvr[4];

Scoreboard sb;

DrvrCovCallback cov_cb;

Packet_channel gen2drvr_chan;

Packet_channel drvr2sb_chan;

Packet_channel rcvr2sb_chan;

function new(virtual mem_interface.MEM mem_intf_new ,

virtual input_interface.IP input_intf_new ,

virtual output_interface.OP output_intf_new[4] );

super.new("Environment ");

this.mem_intf = mem_intf_new ;

this.input_intf = input_intf_new ;

this.output_intf = output_intf_new ;

`vmm_note(this.log, "Created env object");

endfunction : new

virtual function void gen_cfg();

super.gen_cfg();

`vmm_note(this.log,"Start of gen_cfg() method ");

`vmm_note(this.log,"End of gen_cfg() method ");

endfunction

virtual function void build();

super.build();

`vmm_note(this.log,"Start of build() method ");

gen2drvr_chan = new("gen2drvr","chan");

drvr2sb_chan = new("drvr2sb","chan");

rcvr2sb_chan = new("rcvr2sb","chan");

atomic_gen = new("atomic_gen",0,gen2drvr_chan);

atomic_gen.stop_after_n_insts = 10;

drvr = new("Drvr",0,input_intf,gen2drvr_chan,drvr2sb_chan);

foreach(rcvr[i])

rcvr[i] = new($psprintf("Rcvr-%0d",i),i,output_intf[i],rcvr2sb_chan);

sb = new("Sb",0,drvr2sb_chan,rcvr2sb_chan);

cov_cb = new();

drvr.append_callback(cov_cb);

`vmm_note(this.log,"End of build() method ");

endfunction

virtual task reset_dut();

super.reset_dut();

`vmm_note(this.log,"Start of reset_dut() method ");

mem_intf.cb.mem_data <= 0;

mem_intf.cb.mem_add <= 0;

mem_intf.cb.mem_en <= 0;

mem_intf.cb.mem_rd_wr <= 0;

input_intf.cb.data_in <= 0;

input_intf.cb.data_status <= 0;

output_intf[0].cb.read <= 0;

output_intf[1].cb.read <= 0;

output_intf[2].cb.read <= 0;

output_intf[3].cb.read <= 0;

// Reset the DUT

input_intf.reset <= 1;

repeat (4) @ input_intf.clock;

input_intf.reset <= 0;

`vmm_note(this.log,"End of reset_dut() method ");

endtask

virtual task cfg_dut();

super.cfg_dut();

`vmm_note(this.log,"Start of cfg_dut() method ");

mem_intf.cb.mem_en <= 1;

@(posedge mem_intf.clock);

mem_intf.cb.mem_rd_wr <= 1;

@(posedge mem_intf.clock);

mem_intf.cb.mem_add <= 8'h0;

mem_intf.cb.mem_data <= `P0;

`vmm_note(this.log ,$psprintf(" Port 0 Address %h ",`P0));

@(posedge mem_intf.clock);

mem_intf.cb.mem_add <= 8'h1;

mem_intf.cb.mem_data <= `P1;

`vmm_note(this.log ,$psprintf(" Port 1 Address %h ",`P1));

@(posedge mem_intf.clock);

mem_intf.cb.mem_add <= 8'h2;

mem_intf.cb.mem_data <= `P2;

`vmm_note(this.log ,$psprintf(" Port 2 Address %h ",`P2));

@(posedge mem_intf.clock);

mem_intf.cb.mem_add <= 8'h3;

mem_intf.cb.mem_data <= `P3;

`vmm_note(this.log ,$psprintf(" Port 3 Address %h ",`P3));

@(posedge mem_intf.clock);

mem_intf.cb.mem_en <=0;

mem_intf.cb.mem_rd_wr <= 0;

mem_intf.cb.mem_add <= 0;

mem_intf.cb.mem_data <= 0;

`vmm_note(this.log,"End of cfg_dut() method ");

endtask

virtual task start();

super.start();

`vmm_note(this.log,"Start of start() method ");

atomic_gen.start_xactor();

drvr.start_xactor();

rcvr[0].start_xactor();

rcvr[1].start_xactor();

rcvr[2].start_xactor();

rcvr[3].start_xactor();

sb.start_xactor();

`vmm_note(this.log,"End of start() method ");

endtask

virtual task wait_for_end();

super.wait_for_end();

`vmm_note(this.log,"Start of wait_for_end() method ");

repeat(1000) @(input_intf.clock);

`vmm_note(this.log,"End of wait_for_end() method ");

endtask

virtual task stop();

super.stop();

`vmm_note(this.log,"Start of stop() method ");

`vmm_note(this.log,"End of stop() method ");

endtask

virtual task cleanup();

super.cleanup();

`vmm_note(this.log,"Start of cleanup() method ");

`vmm_note(this.log,"End of cleanup() method ");

endtask

virtual task report();

`vmm_note(this.log,"Start of report() method \n\n\n");

$display("---------------------------------------------------------------------");

super.report();

$display("---------------------------------------------------------------------");

$display("\n\n");

`vmm_note(this.log,"End of report() method");

endtask

endclass

`endif

(S)Download the phase 9 score code:

vmm_switch_9.tar

Browse the code in vmm_switch_9.tar

(S)Run the simulation:

vcs -sverilog -f filelist -R -ntb_opts rvm

urg -dir simv.cm/

In this phase we will write the functional coverage for switch protocol. Functional coverage is written in DrvrCovCallback.sv file. After running simulation, you will analyze the coverage results and find out if some test scenarios have not been exercised and write tests to exercise them.

The points which we need to cover are

1) Cover all the port address configurations.

2) Cover all the packet lengths.

3) Cover all correct and incorrect length fields.

4) Cover good and bad FCS.

5) Cover all the above combinations.

We will do the coverage sampling in the driver porst_trans() callback method which we developed in PHASE_6.

1) Define a cover group with following cover points. Define this cover group in a class which extends Driver_callbacks.

class DrvrCovCallback extends Driver_callbacks;

a) All packet lengths:

length : coverpoint pkt.length;

b) All port address:

da : coverpoint pkt.da {

bins p0 = { `P0 };

bins p1 = { `P1 };

bins p2 = { `P2 };

bins p3 = { `P3 }; }

c) Correct and incorrect Length field types:

length_kind : coverpoint pkt.length_kind;

d) Good and Bad FCS:

fcs_kind : coverpoint pkt.fcs_kind;

5) Cross product of all the above cover points:

all_cross: cross length,da,length_kind,fcs_kind;

2) In constructor method, construct the cover group

function new();

switch_coverage = new();

endfunction : new

3) Write task which calls the sample method to cover the points.

task sample(packet pkt);

this.pkt = pkt;

switch_coverage.sample();

endtask:sample

Source Code Of Coverage Class:

`ifndef GUARD_DRVR_CALLBACK_1

`define GUARD_DRVR_CALLBACK_1

class DrvrCovCallback extends Driver_callbacks;

Packet pkt;

covergroup switch_coverage;

length : coverpoint pkt.length;

da : coverpoint pkt.da {

bins p0 = { `P0 };

bins p1 = { `P1 };

bins p2 = { `P2 };

bins p3 = { `P3 }; }

length_kind : coverpoint pkt.length_kind;

fcs_kind : coverpoint pkt.fcs_kind;

all_cross: cross length,da,length_kind,fcs_kind;

endgroup

function new();

switch_coverage = new();

endfunction : new

virtual task post_trans(Packet pkt);

this.pkt = pkt;

switch_coverage.sample();

endtask: post_trans

endclass:DrvrCovCallback

`endif

Now we will connect this callback instance to the Driver.

1) Take the instance of DrvrCovCallback in the Environemtn class.

DrvrCovCallback cov_cb;

2) Construct the cov_cb object in build method.

cov_cb = new();

3) In the Build method, call the append_callback() of the drvr and pass the cov_cb

object.

drvr.append_callback(cov_cb);

(S)Source code of the Environment class:

`ifndef GUARD_ENV

`define GUARD_ENV

class Environment extends vmm_env;

virtual mem_interface.MEM mem_intf ;

virtual input_interface.IP input_intf ;

virtual output_interface.OP output_intf[4] ;

Packet_atomic_gen atomic_gen;

Driver drvr;

Receiver rcvr[4];

Scoreboard sb;

DrvrCovCallback cov_cb;

Packet_channel gen2drvr_chan;

Packet_channel drvr2sb_chan;

Packet_channel rcvr2sb_chan;

function new(virtual mem_interface.MEM mem_intf_new ,

virtual input_interface.IP input_intf_new ,

virtual output_interface.OP output_intf_new[4] );

super.new("Environment ");

this.mem_intf = mem_intf_new ;

this.input_intf = input_intf_new ;

this.output_intf = output_intf_new ;

`vmm_note(this.log, "Created env object");

endfunction : new

virtual function void gen_cfg();

super.gen_cfg();

`vmm_note(this.log,"Start of gen_cfg() method ");

`vmm_note(this.log,"End of gen_cfg() method ");

endfunction

virtual function void build();

super.build();

`vmm_note(this.log,"Start of build() method ");

gen2drvr_chan = new("gen2drvr","chan");

drvr2sb_chan = new("drvr2sb","chan");

rcvr2sb_chan = new("rcvr2sb","chan");

atomic_gen = new("atomic_gen",0,gen2drvr_chan);

atomic_gen.stop_after_n_insts = 10;

drvr = new("Drvr",0,input_intf,gen2drvr_chan,drvr2sb_chan);

foreach(rcvr[i])

rcvr[i] = new($psprintf("Rcvr-%0d",i),i,output_intf[i],rcvr2sb_chan);

sb = new("Sb",0,drvr2sb_chan,rcvr2sb_chan);

cov_cb = new();

drvr.append_callback(cov_cb);

`vmm_note(this.log,"End of build() method ");

endfunction

virtual task reset_dut();

super.reset_dut();

`vmm_note(this.log,"Start of reset_dut() method ");

mem_intf.cb.mem_data <= 0;

mem_intf.cb.mem_add <= 0;

mem_intf.cb.mem_en <= 0;

mem_intf.cb.mem_rd_wr <= 0;

input_intf.cb.data_in <= 0;

input_intf.cb.data_status <= 0;

output_intf[0].cb.read <= 0;

output_intf[1].cb.read <= 0;

output_intf[2].cb.read <= 0;

output_intf[3].cb.read <= 0;

// Reset the DUT

input_intf.reset <= 1;

repeat (4) @ input_intf.clock;

input_intf.reset <= 0;

`vmm_note(this.log,"End of reset_dut() method ");

endtask

virtual task cfg_dut();

super.cfg_dut();

`vmm_note(this.log,"Start of cfg_dut() method ");

mem_intf.cb.mem_en <= 1;

@(posedge mem_intf.clock);

mem_intf.cb.mem_rd_wr <= 1;

@(posedge mem_intf.clock);

mem_intf.cb.mem_add <= 8'h0;

mem_intf.cb.mem_data <= `P0;

`vmm_note(this.log ,$psprintf(" Port 0 Address %h ",`P0));

@(posedge mem_intf.clock);

mem_intf.cb.mem_add <= 8'h1;

mem_intf.cb.mem_data <= `P1;

`vmm_note(this.log ,$psprintf(" Port 1 Address %h ",`P1));

@(posedge mem_intf.clock);

mem_intf.cb.mem_add <= 8'h2;

mem_intf.cb.mem_data <= `P2;

`vmm_note(this.log ,$psprintf(" Port 2 Address %h ",`P2));

@(posedge mem_intf.clock);

mem_intf.cb.mem_add <= 8'h3;

mem_intf.cb.mem_data <= `P3;

`vmm_note(this.log ,$psprintf(" Port 3 Address %h ",`P3));

@(posedge mem_intf.clock);

mem_intf.cb.mem_en <=0;

mem_intf.cb.mem_rd_wr <= 0;

mem_intf.cb.mem_add <= 0;

mem_intf.cb.mem_data <= 0;

`vmm_note(this.log,"End of cfg_dut() method ");

endtask

virtual task start();

super.start();

`vmm_note(this.log,"Start of start() method ");

atomic_gen.start_xactor();

drvr.start_xactor();

rcvr[0].start_xactor();

rcvr[1].start_xactor();

rcvr[2].start_xactor();

rcvr[3].start_xactor();

sb.start_xactor();

`vmm_note(this.log,"End of start() method ");

endtask

virtual task wait_for_end();

super.wait_for_end();

`vmm_note(this.log,"Start of wait_for_end() method ");

repeat(1000) @(input_intf.clock);

`vmm_note(this.log,"End of wait_for_end() method ");

endtask

virtual task stop();

super.stop();

`vmm_note(this.log,"Start of stop() method ");

`vmm_note(this.log,"End of stop() method ");

endtask

virtual task cleanup();

super.cleanup();

`vmm_note(this.log,"Start of cleanup() method ");

`vmm_note(this.log,"End of cleanup() method ");

endtask

virtual task report();

`vmm_note(this.log,"Start of report() method \n\n\n");

$display("---------------------------------------------------------------------");

super.report();

$display("---------------------------------------------------------------------");

$display("\n\n");

`vmm_note(this.log,"End of report() method");

endtask

endclass

`endif

(S)Download the phase 9 score code:

vmm_switch_9.tar

Browse the code in vmm_switch_9.tar

(S)Run the simulation:

vcs -sverilog -f filelist -R -ntb_opts rvm

urg -dir simv.cm/